View troubleshooting beepcodespdf from BIO 4 at Technological Institute of the Philippines. Routine POST Beep Codes.

Best Full Body Workout Best Full Body Workout Fitness Body Victoria Secret Workout

System memory is okay.

. Otherwise it flashes the screen visible bell. Unit SysUtils Unit. More information of uploader 刘强 To Search.

Short beeps are generated for the number in each group. POST error error code shown on screen No beep. If neither alert is possible nothing happens.

Power supply system board problem disconnected CPU or disconnected speaker Continuous beep. 7 Comments 1 Solution 363 Views Last Modified. MSI claims a beep pause double beep during POST is routine for their X48C premimum motherboard when USB devices are connected during BIOS load.

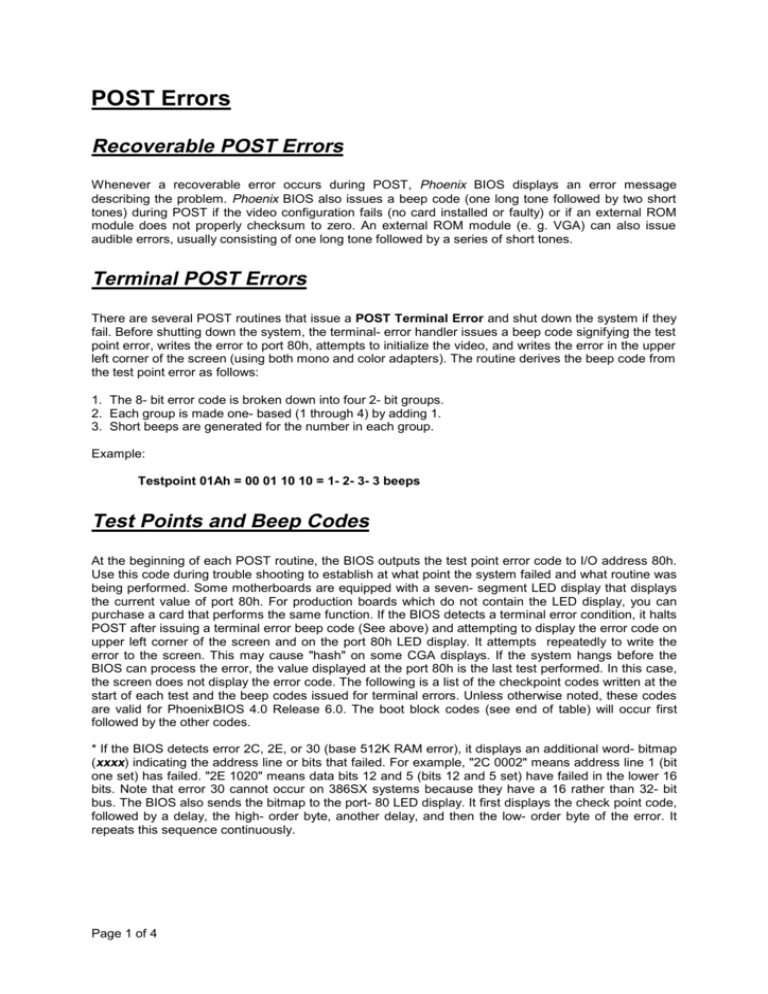

Terminal POST Errors There are several POST routines that require success to. System clock is running. 13 rows Beeps Error Message Description Resolution.

Nearly all terminals have an audible alert bell or beep but only some can flash the screen. RonG2 asked on 1252010. VCL for Win32 Routines.

The routine beep sounds an audible alarm on the terminal if possible. Normal POST system is OK 2 short beeps. Description Definition Delphi 6 2007 2009.

The computer POST power-on self-test checks a computers internal hardware for compatibility and connection before starting the remainder of the boot process. Testpoint 16h 00 01 01 10 1- 2- 2- 3 beeps POST Task Routines. Screen display memory is working.

These checks are called POST and they include. Each group is made one- based 1 through 4 by adding 1. 115 rows The computer POST power-on self-test checks a computers.

3No power loose cord or short. Restore processor control word during warm boot. The routine derives the beep code from the test point error as follows.

July 1 2018. Normal POST computer fine. The routine beep sounds an audible alarm on the terminal if possible.

Sports Outdoors. 8237 DMA controller initialization. To force the buzzer routine 2 to force the video and routines are well worth studying Downloaders recently.

Beep Routine 2 Edit. 8254 timer initialization. 2No power loose card or short.

The 8- bit error code is broken down to four 2- bit groups. BIOS ROM checksum. If the computer passes the POST the computer may give a single beep some computers may beep twice as it starts and continue to boot.

DESCRIPTION The beep and flash routines are used to alert the terminal user. 1No power loose card or short. Power supply system board or keyboard problem 1 long 1 short beep.

POST error review screen for error code. Power supply system board RAM or keyboard problem Repeating short beeps. The routine flash flashes the screen and if that is not possible sounds the alert.

The BIOS does some basic system checks. Initialize cache before memory auto-size. PhoenixBIOS 40 Release 6 POST Task Routines 2 Code Beeps POST Routine Description 0Fh Initialize the local bus IDE 10h Initialize Power Management 11h Load alternate registers with initial POST values 12h Restore CPU control word during warm boot 13h Initialize PCI Bus Mastering devices 14h Initialize keyboard controller 16h 1-2-2-3 BIOS ROM checksum.

Initialize PCI bus mastering devices. Initialize keyboard controller. BIOS is not corrupted.

Beep Routine Edit Edit source History Talk 0 This page is intended as a supplement to the official documentation on Delphi programming. Has anyone heard of this or is MSI trying to avoid. The memory refresh circuitry is.

This all happens very quickly. Components PC Embedded Hardware.

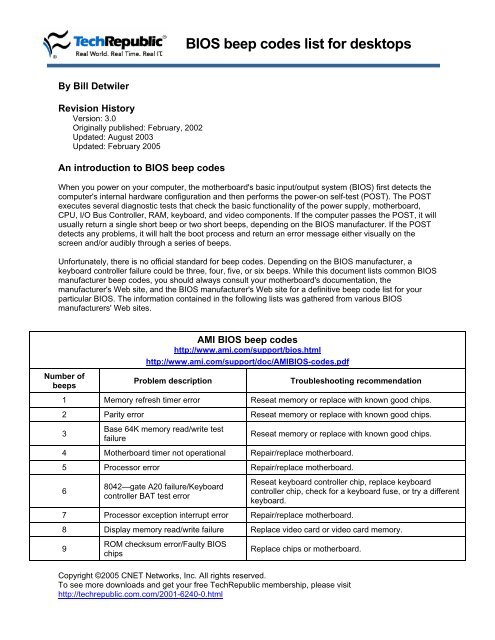

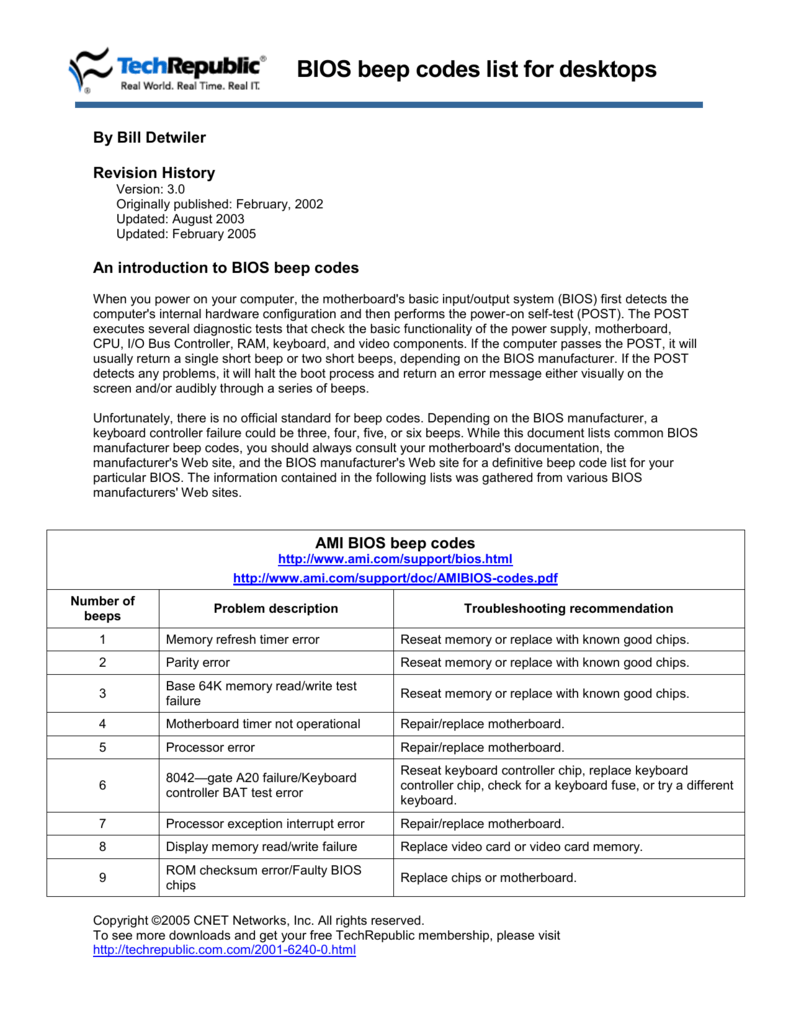

Bios Beep Codes List For Desktops

0 Comments